Abstract

The number of battery-powered devices is rapidly increasing due to the widespread use of IoT-enabled nodes in various fields. Energy harvesters, which help to power embedded devices, are a feasible alternative to replacing battery-powered devices. In a capacitor, the energy harvester stores enough energy to power up the embedded device and compute the task. This type of computation is referred to as intermittent computing. Energy harvesters are unable to supply continuous power to embedded devices. All registers and cache in conventional processors are volatile. We require a Non-Volatile Memory (NVM)-based Non-Volatile Processor (NVP) that can store registers and cache contents during a power failure. NVM-based caches reduce system performance and consume more energy than SRAM-based caches. This paper proposes Efficient Placement and Migration policies for hybrid cache architecture that uses SRAM and STT-RAM at the first level cache. The proposed architecture includes cache block placement and migration policies to reduce the number of writes to STT-RAM. During a power failure, the backup strategy identifies and migrates the critical blocks from SRAM to STT-RAM. When compared to the baseline architecture, the proposed architecture reduces STT-RAM writes from 63.35% to 35.93%, resulting in a 32.85% performance gain and a 23.42% reduction in energy consumption. Our backup strategy reduces backup time by 34.46% when compared to the baseline.

Similar content being viewed by others

References

Golpîra H, Khan SAR, Safaeipour S (2021) A review of logistics internet-of-things: current trends and scope for future research. J Ind Inf Integr 22:100194

Hu X, Xu L, Lin X, Pecht M (2020) Battery lifetime prognostics. Joule 4(2):310–346

Ma D, Lan G, Hassan M, Hu W, Das SK (2019) Sensing, computing, and communications for energy harvesting iots: a survey. IEEE Commun Surv Tutor 22(2):1222–1250

Mamen A, Supatti U (2017) A survey of hybrid energy storage systems applied for intermittent renewable energy systems. In: 2017 14th international conference on electrical engineering/electronics, computer, telecommunications and information technology (ECTI-CON), pp. 729– 732. IEEE

Liu Y, Li H, Li X, Xue JC, Xie Y, Yang H (2015) Self-powered wearable sensor node: challenges and opportunities. In: International conference on compilers, architecture and synthesis for embedded systems, pp. 189– 189. IEEE

Martinez B, Monton M, Vilajosana I, Prades JD (2015) The power of models: modeling power consumption for iot devices. IEEE Sens J 15(10):5777–5789

Lucia B, Balaji V, Colin A, Maeng K, Ruppel E (2017) Intermittent computing: challenges and opportunities. 2nd Summit on Advances in Programming Languages (SNAPL 2017)

Surbatovich M, Lucia B, Jia L (2020) Towards a formal foundation of intermittent computing. Proc ACM Program Lang 4:1–31

Hester J, Sorber J (2017) The future of sensing is batteryless, intermittent, and awesome. In: Proceedings of the 15th ACM conference on embedded network sensor systems, pp. 1– 6

Jog A, Mishra AK, Xu C, Xie Y, Narayanan V, Iyer R, Das CR (2012) Cache revive: architecting volatile stt-ram caches for enhanced performance in cmps. In: Design automation conference, pp. 243– 252 . IEEE

Manohar SS, Kapoor HK (2022) Capmig: coherence aware block placement and migration in multi-retention stt-ram caches. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

Sarkar A, Singh N, Venkitaraman V, Singh V (2021) Dam: deadblock aware migration techniques for stt-ram-based hybrid caches. IEEE Comput Archit Lett 20(1):62–4

Agarwal S, Chakraborty S (2021) Abaca: access based allocation on set wise multi-retention in stt-ram last level cache. In: 2021 IEEE 32nd international conference on application-specific systems, architectures and processors (ASAP), pp. 171– 174 . IEEE

Pan C, Xie M, Hu J, Chen Y, Yang C (2014) 3m-pcm: Exploiting multiple write modes mlc phase change main memory in embedded systems. In: Proceedings of the international conference on hardware/software codesign and system synthesis, pp. 1– 10

Lee A, Lo C-P et al (2017) A reram-based nonvolatile flip-flop with self-write-termination scheme for frequent-off fast-wake-up nonvolatile processors. IEEE J Solid-State Circuits 52(8):2194–2207

Instruments T (2018) MSP430FR5969 launchpad development kit

Wang Z, Jiménez DA, Xu C, Sun G, Xie Y (2014) Adaptive placement and migration policy for an stt-ram-based hybrid cache. In: IEEE 20th international symposium on high performance computer architecture, pp. 13– 24. IEEE

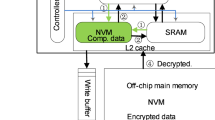

Xie M, Pan C, Zhang Y, Hu J, Liu Y, Xue CJ (2018) A novel stt-ram-based hybrid cache for intermittently powered processors in iot devices. IEEE Micro 39(1):24–32

Ma K, Zheng Y, Li S, Swaminathan K, Li X, Liu Y, Sampson J, Xie Y, Narayanan V (2015) Architecture exploration for ambient energy harvesting nonvolatile processors. In: IEEE 21st international symposium on high performance computer architecture, pp. 526– 537. IEEE

Mao M, Li H, Jones AK, Chen Y (2013) Coordinating prefetching and stt-ram based last-level cache management for multicore systems. In: Proceedings of the 23rd ACM international conference on great lakes symposium on VLSI, pp. 55– 60. ACM New York, NY, USA

Sun Z, Bi X, Li H, Wong W-F, Ong Z-L, Zhu X, Wu W (2011) Multi retention level stt-ram cache designs with a dynamic refresh scheme. In: Proceedings of the 44th annual IEEE/ACM international symposium on microarchitecture, pp. 329– 338. ACM New York, NY, USA

Smullen CW, Mohan V, Nigam A, Gurumurthi S, Stan MR (2011) Relaxing non-volatility for fast and energy-efficient stt-ram caches. In: IEEE 17th international symposium on high performance computer architecture, pp. 50– 61. IEEE

Li H, Liu Y, Zhao Q, Gu Y, Sheng X, Sun G, Zhang C, Chang M-F, Luo R, Yang H (2015) An energy efficient backup scheme with low inrush current for nonvolatile sram in energy harvesting sensor nodes. In: Design, Automation & Test in Europe Conference & Exhibition, pp. 7– 12. IEEE

Wu X, Li J, Zhang L, Speight E, Rajamony R, Xie Y (2010) Design exploration of hybrid caches with disparate memory technologies. ACM Trans Arch Code Optim 7(3):1–34

Kim N, Ahn J, Choi K, Sanchez D, Yoo D, Ryu S (2018) Benzene: an energy-efficient distributed hybrid cache architecture for manycore systems. ACM Trans Arch Code Optim 15(1):1–23

Zhao J, Xu C, Zhang T, Xie Y (2016) Bach: a bandwidth-aware hybrid cache hierarchy design with nonvolatile memories. J Comput Sci Technol 31(1):20–35

Ahn J, Yoo S, Choi K (2015) Prediction hybrid cache: an energy-efficient stt-ram cache architecture. IEEE Trans Comput 65(3):940–951

Gao L, Wang R, Xu Y, Yang H, Luan Z, Qian D, Zhang H, Cai J (2018) Sram-and stt-ram-based hybrid, shared last-level cache for on-chip cpu-gpu heterogeneous architectures. J Supercomput 74(7):3388–3414

Yao J, Ma J, Chen T, Hu T (2013) An energy-efficient scheme for stt-ram l1 cache. In: IEEE 10th international conference on high performance computing and communications & 2013 IEEE International Conference on Embedded and Ubiquitous Computing, pp. 1345– 1350. IEEE

Xie M, Zhao M, Pan C, Hu J, Liu Y, Xue CJ (2015) Fixing the broken time machine: Consistency-aware checkpointing for energy harvesting powered non-volatile processor. In: Proceedings of the 52nd annual design automation conference, pp. 1– 6. ACM New York, NY, USA

Liu Y, Suy F, Wangy Z, Yang H (2015) Design exploration of inrush current aware controller for nonvolatile processor. In: 2015 IEEE Non-volatile memory system and applications symposium, pp. 1– 6. IEEE

Zhou Y, Zhao M, Ju L, Xue CJ, Li X, Jia Z (2017) Energy-aware morphable cache management for self-powered non-volatile processors. In: IEEE 23rd international conference on embedded and real-time computing systems and applications, pp. 1– 7. IEEE

Xie M, Zhao M, Pan C, Li H, Liu Y, Zhang Y, Xue CJ, Hu J (2016) Checkpoint aware hybrid cache architecture for nv processor in energy harvesting powered systems. In: International conference on hardware/software codesign and system synthesis, pp. 1– 10. IEEE

Ransford B, Sorber J, Fu K (2011) Mementos: System support for long-running computation on rfid-scale devices. In: Proceedings of the sixteenth international conference on architectural support for programming languages and operating systems, pp. 159– 170

Balsamo D, Weddell AS, Das A, Arreola AR, Brunelli D, Al-Hashimi BM, Merrett GV, Benini L (2016) Hibernus++: a self-calibrating and adaptive system for transiently-powered embedded devices. IEEE Trans Comput Aided Des Integr Circuits Syst 35(12):1968–1980

Kortbeek V, Yildirim KS, Bakar A, Sorber J, Hester J, Pawełczak P (2020) Time-sensitive intermittent computing meets legacy software. In: Proceedings of the twenty-fifth international conference on architectural support for programming languages and operating systems, pp. 85– 99

Su F, Liu Y, Wang Y, Yang H (2016) A ferroelectric nonvolatile processor with 46 \( \backslash \mu \) s system-level wake-up time and 14\( \backslash \mu \) s sleep time for energy harvesting applications. IEEE Trans Circuits Syst I Regul Pap 64(3):596–607

Choi J, Joe H, Kim Y, Jung C (2019) Achieving stagnation-free intermittent computation with boundary-free adaptive execution. In: IEEE real-time and embedded technology and applications symposium, pp. 331– 344 . IEEE

Binkert N, Beckmann B, Black G, Reinhardt SK, Saidi A, Basu A, Hestness J, Hower DR, Krishna T, Sardashti S et al (2011) The gem5 simulator. ACM SIGARCH Comput Arch news 39(2):1–7

Sun G, Dong X, Xie Y, Li J, Chen Y (2009) A novel architecture of the 3d stacked mram l2 cache for cmps. In: IEEE 15th international symposium on high performance computer architecture, pp. 239– 249 . IEEE

Wu X, Li J, Zhang L, Speight E, Rajamony R, Xie Y (2009) Hybrid cache architecture with disparate memory technologies. ACM SIGARCH Comput Arch News 37(3):34–45

Li J, Xue CJ, Xu Y (2011) Stt-ram based energy-efficiency hybrid cache for cmps. In: IEEE/IFIP 19th International Conference on VLSI and System-on-Chip, pp. 31– 36 . IEEE

Jadidi A, Arjomand M, Sarbazi-Azad H (2011) High-endurance and performance-efficient design of hybrid cache architectures through adaptive line replacement. In: IEEE/ACM International Symposium on Low Power Electronics and Design, pp. 79– 84 . IEEE

Choi J-H, Park G-H (2017) Nvm way allocation scheme to reduce nvm writes for hybrid cache architecture in chip-multiprocessors. IEEE Trans Parallel Distrib Syst 28(10):2896–2910

Guthaus MR, Ringenberg JS, Ernst D, Austin TM, Mudge T, Brown RB (2001) Mibench: a free, commercially representative embedded benchmark suite. In: Proceedings of the Fourth Annual IEEE International Workshop on Workload Characterization, pp. 3– 14 . IEEE

Dong X, Xu C, Xie Y, Jouppi NP (2012) Nvsim: a circuit-level performance, energy, and area model for emerging nonvolatile memory. IEEE Trans Comput Aided Des Integr Circuits Syst 31(7):994–1007

Acknowledgements

This work is supported by the grant received from the Department of Science and Technology, Govt. of India, for the Technology Innovation Hub at the IIT Ropar in the framework of the National Mission on Interdisciplinary Cyber-Physical Systems.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Badri, S., Saini, M. & Goel, N. Efficient placement and migration policies for an STT-RAM based hybrid L1 cache for intermittently powered systems. Des Autom Embed Syst 27, 303–331 (2023). https://doi.org/10.1007/s10617-023-09272-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10617-023-09272-w