Abstract

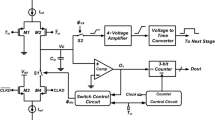

This article proposes a two-stage time-to-digital converter with a novel method for enhancing resolution and using digital error correction called time-to-digital converter with enhanced resolution (TDC-ER). The proposed TDC is composed of two Vernier TDCs and operating in two stages. The first stage uses a normal Vernier TDC with a 512 ps range, and the second stage employs a 2D Vernier TDC with a new delay element. The second stage can achieve a fine resolution of 2 ps. This study presents a novel idea for boosting the resolution by analyzing D flip-flop (DFF) outputs in the metastability state. In the end, it is shown that this method can achieve a 1 ps resolution. The TDC-ER offers the benefits of new digital error correction, reducing the connection error between two stages and increasing linearity. A new calibration idea is presented in this work. This circuit is designed and simulated using a 65-nm standard CMOS technology, and the simulation result demonstrates a 1.56 ps effective resolution and a 9-bit range. It operates at 250 MS/s while consuming about 0.5 mW power from a 1.2-V supply.

Similar content being viewed by others

References

Caram JP, Galloway J, Kenney JS (2018) Time-to-digital converter with sample-and-hold and quantization noise scrambling using harmonics in ring oscillators. IEEE Trans Circuits Syst I Regul Pap 65(1):74–83

Chandrasekaran ST, Jayaraj A, Danesh M, Sanyal A (2018) A highly digital second-order oversampling TDC. IEEE Solid-State Circuits Lett 1(5):114–117

Chen C-C, Chen P, Hwang C-S, Chang W (2005) A precise cyclic CMOS time-to-digital with low thermal sensitivity converter. IEEE Trans Nucl Sci 52(4):834–838

Chen CC, Hwang CS, Liu KC, Chen GH (2014) CMOS time-to-digital converter based on a pulse-mixing scheme. IEEE Trans Circuits Syst II 85(11):163–167

Chen H et al (2019) Development of a time-of-flight electronics system for neutron beam profiling at CSNS-WNS. IEEE Trans Nucl Sci 66(8):2005–2010

Enomoto R, Iizuka T, Koga T, Nakura T, Asada K (2018) A 16-bit 2.0-ps resolution two-step TDC in 0.18-µm CMOS utilizing pulse-shrinking fine stage with built-in coarse. IEEE Trans Very Large Scale Integr 27(1):11–19

Fathi M, Sheikhaei S (2020) A SAR ADC based time-to-digital converter in CMOS technology. In: 28th Iranian conference on electrical engineering, no 1, pp 1–5

Filanovsky IM, Allam A (2001) Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits. IEEE Trans Circuits Syst I Fundam Theory Appl 48(7):876–884

Fish A, Mosheyev V, Linkovsky V, Yadid-Pecht O (2004) Ultra-low-power off based shift registers design for CMOS image sensors applications. In: 11th IEEE international conference on electronics, circuits and systems, ICECS, pp 658–661

Hussein AI, Member S, Vasadi S, Paramesh J, Member S (2018) A 450 fs 65-nm CMOS millimeter-wave time-to-digital converter using statistical element selection for all-digital PLLs. IEEE J Solid-State Circuits 53(2):357–374

Kim D, Kim K, Yu W, Cho S (2019) A second-order ΔΣ time-to-digital converter using highly digital time-domain arithmetic circuits. IEEE Trans Circuits Syst II Express Br 66(10):1643–1647

Lee M, Abidi AA (2008) A9 b, 1.25 ps resolution coarse-fine time-to-digital converter in 90 nm CMOS that amplifies a time residue. IEEE J Solid-State Circuits 43(4):769–777

Levine PM, Roberts GW (2004) A calibration technique for a high-resolution flash time-to-digital converter. Int Symp Circuits Syst 1:7–10

Liao D, Wang H, Dai FF, Xu Y, Berenguer R, Hermoso SM (2017) An 802.11a/b/g/n digital fractional-N PLL with automatic TDC linearity calibration for spur cancellation. IEEE J Solid-State Circuits 52(5):1210–1220

Lu P, Wu Y, Andreani P (2015) A 2.2ps 2-D gated-vernier time-to-digita converter with digital calibration. IEEE Trans Circuits Syst II 63(11):1019–1023

Määttä K, Kostamovaara J (1998) A high-precision time-to-digital converter for pulsed time-of-flight laser radar applications. IEEE Trans Instrum Meas 47(2):521–536

Molaei H, Hajsadeghi K (2019) A 5.3-ps, 8-b time to digital converter using a new gain-reconfigurable time amplifier. IEEE Trans Circuits Syst II Express Br 66(3):352–356

Seo MW et al (2016) A 10 ps time-resolution CMOS image sensor with two-tap true-CDS lock-in pixels for fluorescence lifetime imaging. IEEE J Solid-State Circuits 51(1):141–154

Vercesi L, Liscidini A, Castello R (2010) Two-dimensions vernier time-to-digital converter. IEEE J Solid-State Circuits 45(8):1504–1512

Wang H, Dai FF, Wang H (2018) A reconfigurable vernier time-to-digital converter with 2-D spiral comparator array and second-order ΔΣ linearization. IEEE J Solid-State Circuits 53(3):738–749

Yi X, Liang Z, Boon CC, Feng G, Meng F, Yang K (2020) An inverted ring oscillator noise-shaping time-to-digital converter with in-band noise reduction and coherent noise cancellation. IEEE Trans Circuits Syst I Regul Pap 67(2):686–698

Ziabakhsh S, Gagnon G, Roberts GW (2019) A second-order bandpass ΔΣ time-to-digital converter with negative time-mode feedback. IEEE Trans Circuits Syst I Regul Pap 66(4):1355–1368

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Fathi, M., Sheikhaei, S. Two-Stage Vernier-Based Time-to-Digital Converter with Enhanced Resolution and Digital Error Correction. Iran J Sci Technol Trans Electr Eng (2024). https://doi.org/10.1007/s40998-024-00707-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s40998-024-00707-z